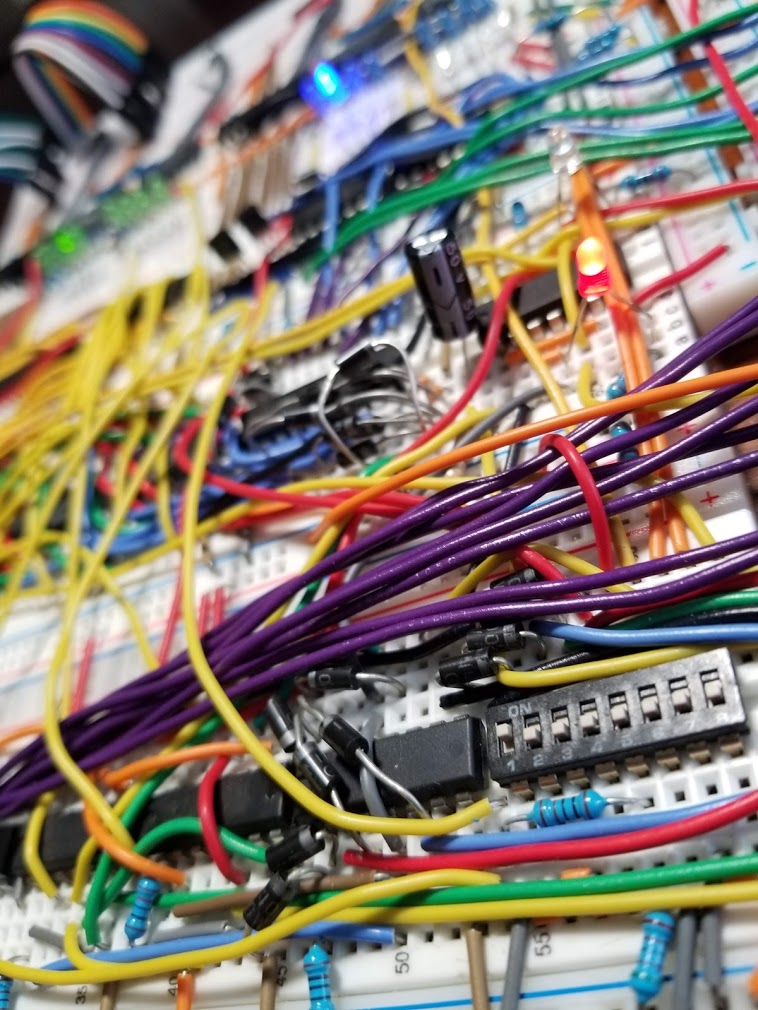

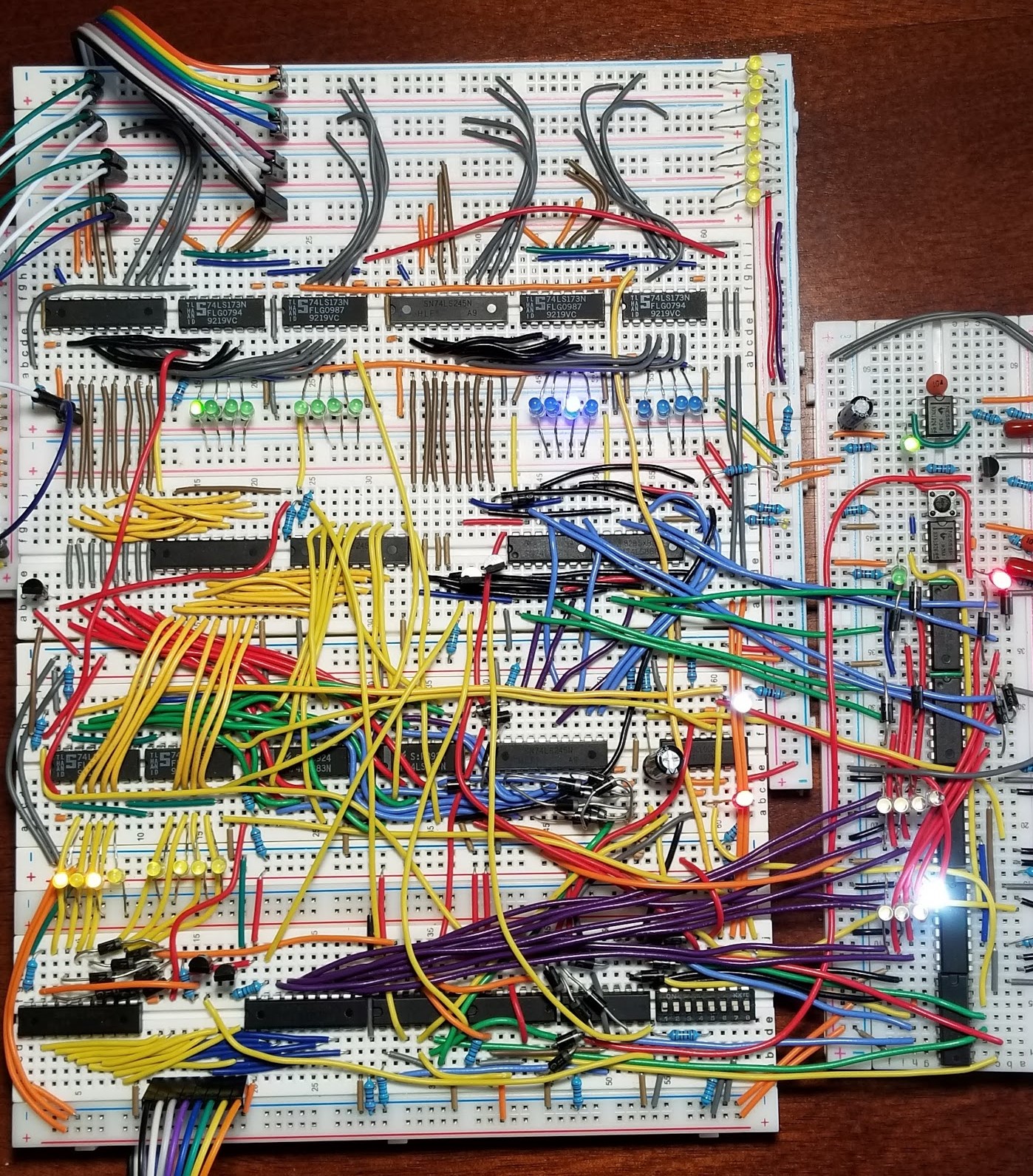

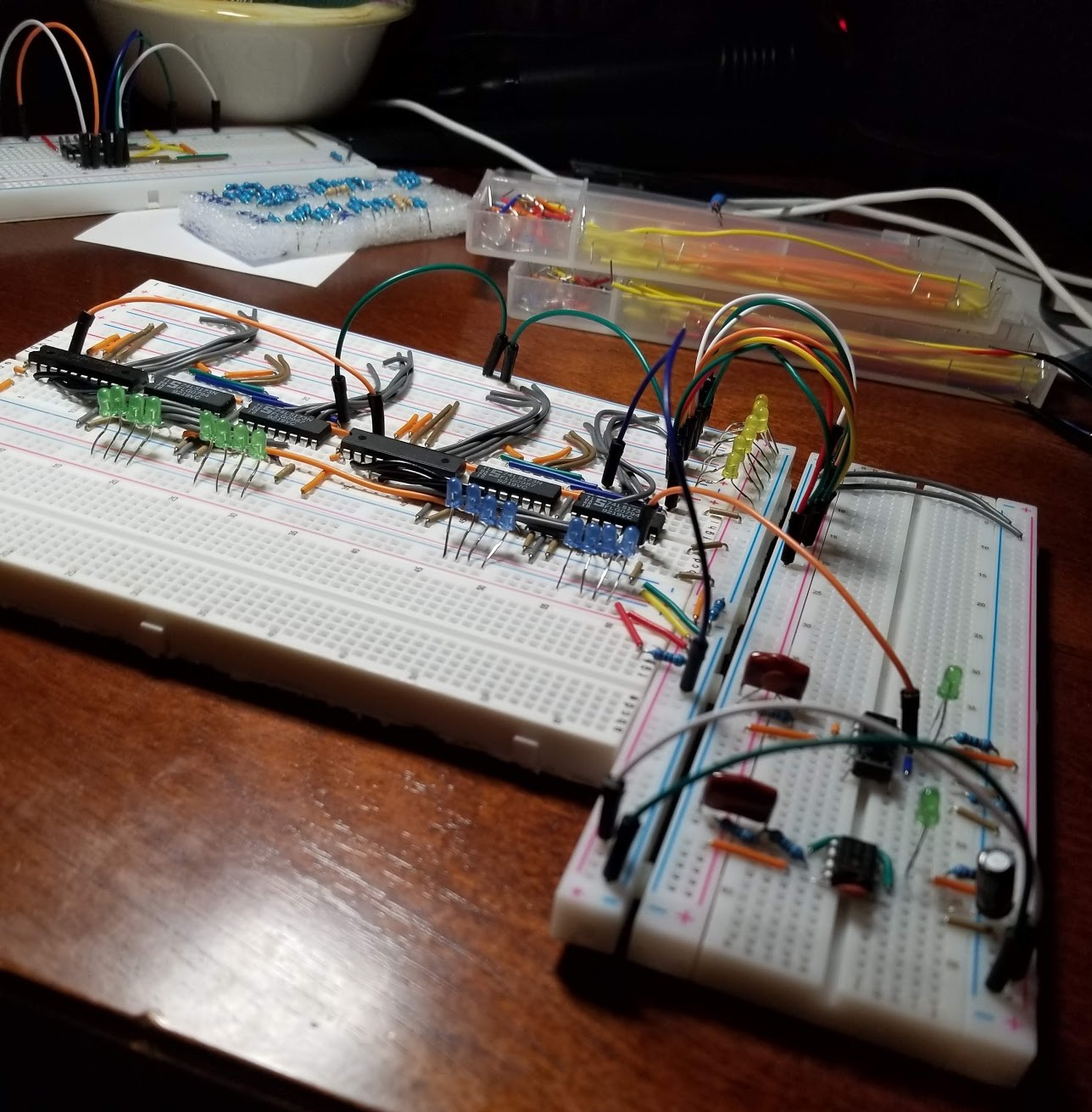

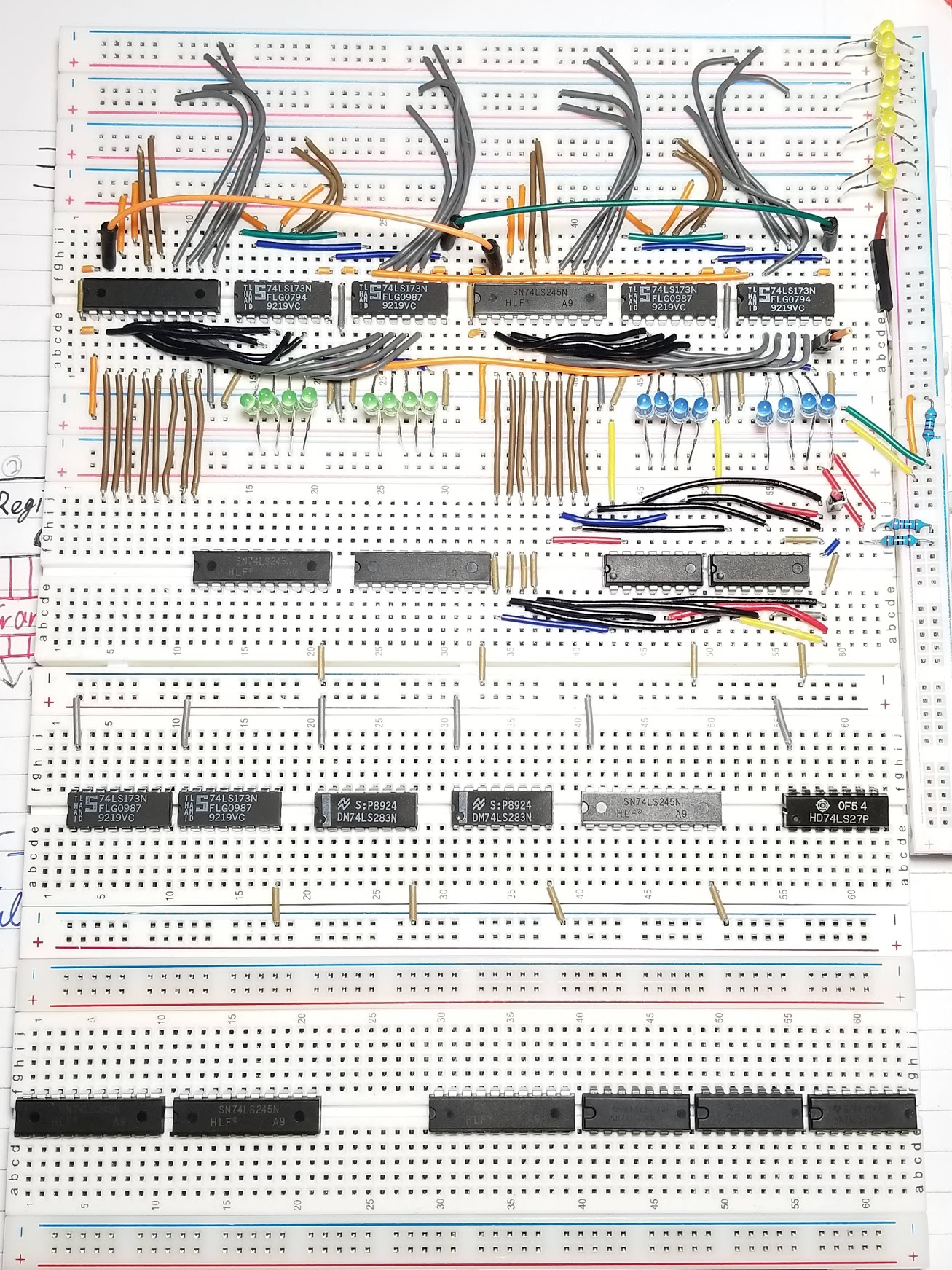

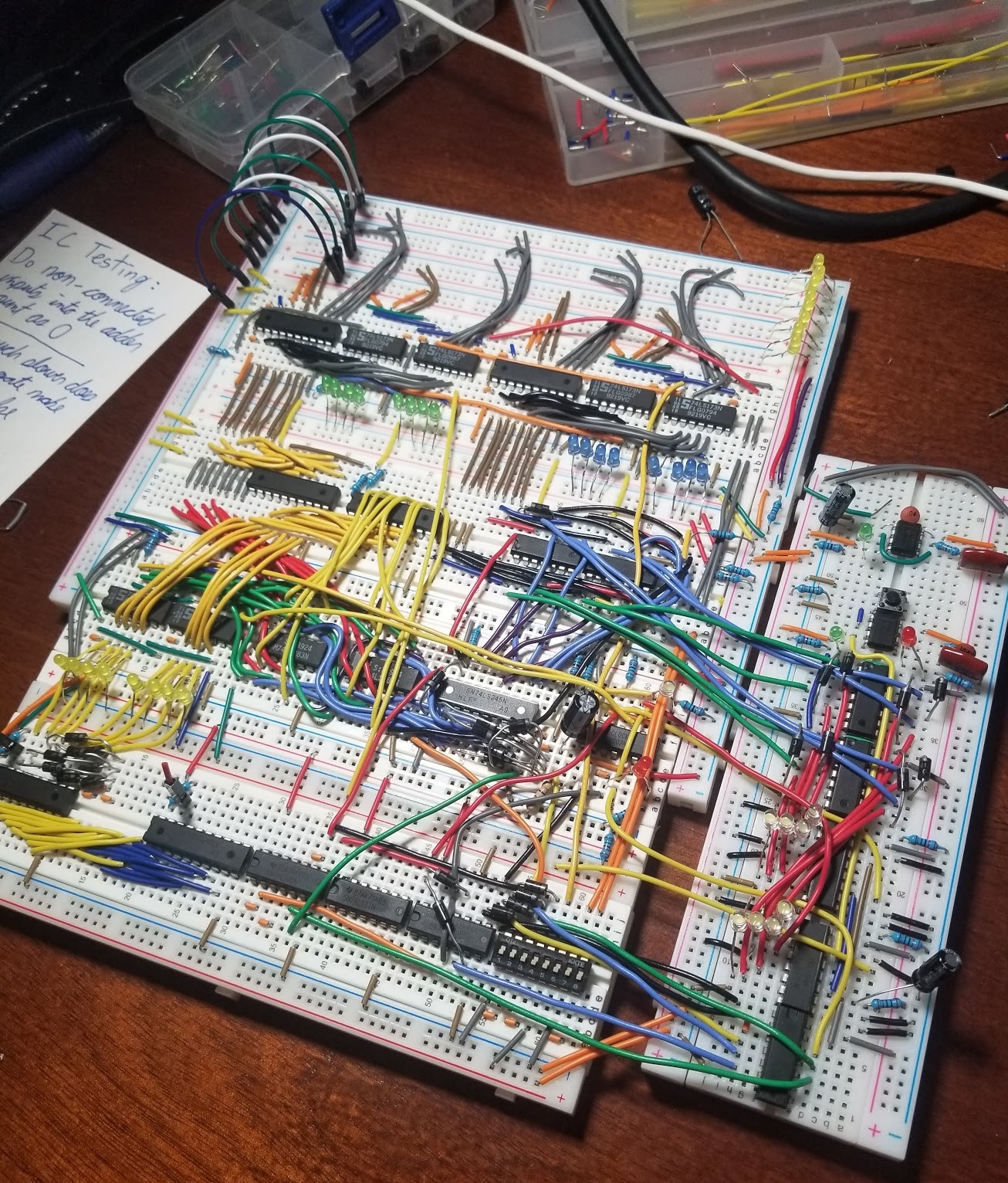

Arithmetic begins after registers A and B have been loaded with their respective operands. The addition of the ALU is taken care of by the coupled 4-bit Binary Adders, located in the center of the mass wire cluster on the board. For subtraction, XOR gate ICs are used for the logic inversion of register B, and the carry-in of the adder is set high, in order to apply the two’s complement subtraction method.

Multiplication is accomplished by adding the number from register A an amount of register B times. For division, the operand of register B is subtracted into register A repeatedly until register A becomes zero. The total number of subtractions is counted which is the answer to the division. Because multiplication and division require repeated use of the 74LS283 adder, multiple clock cycles are required for the completion of an operation.

The user interface consists of an eight-input dip switch and an attached input station for the bus lines at the top of the ALU for easy initialization of registers A and B.